Low Cost Boundary Scan Tester

This project uses the SKP16C62P (SKP) to implement a JTAG – Boundary Scan interface to an Altera complex programmable logic device – CPLD (part number EPM7128S). The SKP can execute boundary scan commands to the CPLD. For example, firmware can read the CPLD device ID via the JTAG port. The firmware can also assert selected outputs and read inputs on the CPLD, and this does not require a programmed CPLD.

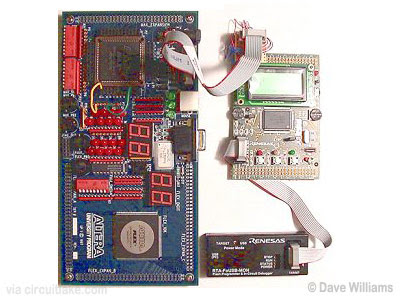

The Altera EPM7128S is mounted on a demo board that contains a header to each CPLD I/O. The Altera Demo board is a denoted University Board that the author has used for teaching HDL (Verilog/VHDL) programming of PLDs. The user can wire to various devices such as light-emitting diodes (LEDs). The firmware included in my project drives some chosen I/O low to illuminate selected LEDs.

The JTAG (Joint Test Action Group) interface is wire-wrap construction using a perf board that contains a 2 x 5 header. This header accommodates a cable that mates to the Altera demo board and completes the JTAG interface. The Altera CPLD is powered entirely from 5V. And since the 16C62P microcontroller has 5V I/O, no level shifting is required.

There are 3 main pieces of hardware for this project: the SKP demo board, the Altera CPLD demo board and an interface cable.